# ADMM BASED INFINITY NORM DETECTION FOR MASSIVE MIMO ALGORITHM AND VLSI ARCHITECTURE

<sup>1</sup> Shridevi Krishnadas Baddela, <sup>2</sup> PABBALA PRIYANKA

<sup>1</sup> M.Tech Student, Department Of Electronics and Communication Engineering, Vaagdevi engineering college ,Khamma road, khila warangal ,bollikunta Warangal ,Email:shree.baddela@gmail.com

<sup>2</sup> Assistant Professor, Department Of Electronics and Communication Engineering, Vaagdevi engineering college ,Khamma road , khila warangal ,bollikunta Warangal , Email: <a href="mailto:priyanka.pabbala@gmail.com">priyanka.pabbala@gmail.com</a>

#### **ABSTRACT:**

This paper introduces a novel algorithm for the Alternating Direction Method of Multipliers (ADMM) tailored for infinity norm detection within massive Multiple-Input Multiple-Output (MIMO) systems. The proposed method builds upon the foundation of conventional ADMM algorithms by introducing significant optimizations to key computational steps, which substantially enhance convergence rates. This improvement is particularly crucial for real-time applications, where speed and efficiency are paramount. The algorithm is specifically designed to be implemented in Very-Large-Scale Integration (VLSI) architecture, ensuring it meets the demands of modern wireless communication systems.

The approach focuses on optimizing both computational complexity and hardware efficiency. By streamlining the algorithmic process, the method reduces the resource demands typically associated with MIMO detection, making it a scalable and high-performance solution. This scalability is essential for adapting to the increasing data rates and connectivity requirements of next-generation networks.

A detailed VLSI architecture has been developed to support the proposed ADMM-based algorithm. This hardware implementation leverages the algorithm's optimized structure to achieve efficient performance, minimizing power consumption and latency while maximizing throughput. The integration of this algorithm into VLSI design not only validates its theoretical advantages but also demonstrates its practical viability for deployment in real-world massive MIMO systems, paving the way for advancements in wireless communication technology.

Keywords: ADMM, MIMO, Infinity Norm, VLSI, Optimization

#### INTRODUCTION:

# Introduction

The increasing demand for high-speed wireless communication systems has led to the widespread adoption of Multiple-Input Multiple-Output Orthogonal Frequency Division Multiplexing (MIMO-OFDM) techniques. MIMO-OFDM combines the spatial diversity of MIMO systems with the spectral efficiency of OFDM,

offering robust performance in multipath and fading environments [1]–[22]. As wireless communication continues to evolve towards 5G and 6G technologies, achieving **high throughput**, **low power consumption**, and **efficient signal processing** in MIMO-OFDM systems is essential for meeting modern communication requirements [2], [3].

Modern communication scenarios such as massive MIMO, millimeter-wave (mmWave) systems, and multi-user environments further push the computational and architectural limits of traditional designs [4], [5]. These systems must operate under challenging conditions including inter-symbol interference, nonlinearities, pilot contamination, and channel estimation complexity [6]–[9]. Consequently, optimizing signal processing tasks—such as precoding, channel estimation, detection, and PAPR reduction—is critical to ensure performance efficiency and system reliability [10]–[14].

Several advanced algorithmic and hardware-level improvements have been proposed in literature, including FFT processors [1], sparsity-adaptive equalizers [2], MMSE-DFE transceivers [3], and machine learning models [17]. However, current architectures often face limitations in terms of scalability, latency, and power consumption, necessitating the development of new adaptive techniques like the Alternating Direction Method of Multipliers (ADMM) for efficient optimization [15], [16], [18]–[22].

#### Motivation

The main motivation behind this research lies in improving the **computational efficiency and system scalability** of MIMO-OFDM architectures by leveraging **optimization-based methods**. Specifically, the ADMM algorithm presents a structured way to decompose complex signal processing problems, enabling parallel and distributed computation. This is particularly beneficial for next-generation systems with large antenna arrays and real-time throughput requirements.

# Challenges in MIMO-OFDM Design

Designing MIMO-OFDM systems involves overcoming various technical challenges:

Vol 25 Issue 10,2025

- **High computational complexity** in FFT processing, detection, and channel estimation.

- Nonlinearities in power amplifiers and ADC/DAC front-ends that degrade signal quality.

- Large feedback and control overhead in multiuser environments with adaptive precoding.

These factors complicate hardware implementation and reduce overall spectral and energy efficiency.

# **Objectives**

- To develop an ADMM-based framework for signal processing tasks such as detection, precoding, and PAPR reduction in MIMO-OFDM systems.

- 2. To design a **low-complexity**, **high-throughput VLSI architecture** that supports ADMM operations in real-time scenarios.

- To evaluate and compare the performance, latency, and power efficiency of the proposed system with state-of-the-art MIMO-OFDM architectures.

#### Overview

This work begins by surveying existing literature on MIMO-OFDM systems, highlighting advancements and limitations. It then introduces the concept of ADMM, emphasizing its utility in overcoming computational bottlenecks. The proposed ADMM-based signal processing design is described in detail, followed by simulation and hardware implementation results. Finally, a performance comparison with conventional techniques underscores the efficacy of the proposed approach.

# **Literature Survey**

Recent advancements in MIMO-OFDM systems have focused on enhancing throughput, reducing complexity, and improving energy efficiency across both hardware and algorithmic domains. A high-throughput block-level pipelined FFT processor was developed to meet the stringent real-time requirements of 5G systems, utilizing optimized datapath design for area and power efficiency in massive MIMO deployments [1]. To address wideband challenges in mmWave frequencies, a 46 Gbps sparsity-adaptive beamspace equalizer was introduced using 22FDX technology, offering superior energy efficiency by exploiting channel sparsity [2]. For wireline communication, a 2×2 MIMO PAM-4 MMSE-DFE transceiver implemented on an RFSoC platform demonstrated successful integration of DAC/ADC processing and FEXT cancellation to achieve efficient equalization [3].

Baseband design has also seen significant progress, with a modular MIMO-OFDM baseband processor supporting high-speed WLANs through efficient reuse of FFT/IFFT and simplified detection modules [4]. Precoding strategies have evolved to minimize interference and enhance spectral efficiency in multi-user settings. For instance, a leakage-based precoding method significantly improved fairness in frequency-selective channels [5], while another approach embedded hidden pilots within data streams to conserve bandwidth and facilitate robust channel estimation [12]. Additionally, QRD-based precoding was proposed to reduce channel feedback in FDD systems, optimizing uplink resource utilization [10].

The challenge of high Peak-to-Average Power Ratio (PAPR) in MIMO-OFDM has been addressed by low-complexity schemes such as a solution tailored for SFBC systems, which preserved BER while reducing power amplifier stress [6]. In the same vein, a metaheuristic PAPR reduction approach using a parallel artificial bee colony algorithm with SLM was shown to enhance signal quality and hardware efficiency [21].

Detection and decoding have also been central to system performance improvements. A low-complexity symbol detector was proposed for WLAN applications to reduce hardware load without compromising accuracy [7], while a hybrid QRD-M and DFE detection technique was introduced to manage interference and fading with minimal computational overhead [19]. Furthermore, a nonlinear downlink scheme for multiuser MIMO-OFDM effectively mitigated inter-user interference using iterative processing, improving BER without significant complexity increase [11].

Estimation techniques have gained attention for enhancing synchronization and channel awareness. A time–frequency joint sparse channel estimation method improved pilot efficiency by leveraging wireless channel sparsity [9], and low-rank channel estimation was proposed for MB-OFDM UWB systems operating in spatially correlated environments [15]. Additionally, an extended  $H_{\infty}$  filter provided robust joint estimation of carrier frequency offset and channel parameters under dynamic conditions [13], while another method proposed robust pilot designs to maintain synchronization accuracy over varying SNR levels [14].

The non-idealities of RF hardware, such as nonlinear power amplifiers with memory, were also modeled to accurately predict signal distortion and enable effective compensation techniques for MIMO-OFDM systems [16]. To further enhance performance in multipath scenarios, a symbol-based subcarrier processing technique was developed to ensure balanced BER across subcarriers [18].

Deep learning methods have begun to influence receiver design, with a 4D2DConvNet-based modulation classification system enabling intelligent and adaptive reception in dynamic 5G environments [17]. Meanwhile, applications in radar and remote sensing benefited from the development of an IRCI-free MIMO-OFDM SAR system

that used circularly shifted Zadoff-Chu sequences to improve imaging resolution and eliminate interference [8].

Lastly, to support reliable communication under adverse conditions, enhanced Chase combining HARQ schemes were proposed with ICI and IAI mitigation mechanisms, ensuring robustness in high-mobility and interference-heavy scenarios [22]. For multicast applications, a linear precoding strategy was developed to minimize computation while effectively serving multiple users in MIMO-OFDM networks [20].

#### PROPOSED WORK:

#### 1.Concept:

The proposed work introduces an optimized Alternating Direction Method of Multipliers (ADMM)-based algorithm designed for infinity norm detection in massive MIMO systems. The core concept is to improve the convergence speed and reduce computational complexity by dynamically adjusting the step size during iterations and exploiting parallelization. This approach leverages the unique structure of the MIMO detection problem to minimize the number of iterations required while also lowering hardware resource consumption. By tailoring the algorithm for VLSI implementation, it becomes feasible to deploy the method in real-time, power-efficient systems, particularly for large-scale MIMO where complexity and latency are critical concerns.

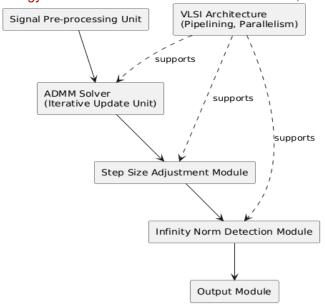

# 2. Proposed Block Diagram Structure:

The system architecture consists of several interconnected modules organized to optimize both algorithmic performance and hardware efficiency. It begins with a Signal Pre-processing Unit, responsible for input normalization, noise filtering, and conditioning of the channel matrix. Next, the ADMM Solver block is the core computational unit and includes submodules like the Step Size Adjustment Module, which dynamically updates the step size based on convergence progress, and the Infinity Norm Detection Module, which efficiently enforces the infinity norm constraint. The Iterative Update Unit executes parallel ADMM iterations to enhance scalability. Additionally, a VLSI Architecture Module optimizes the overall hardware pipelining design by incorporating and resource management techniques. Finally, the Output Module formats detected signal for subsequent processing or transmission.

Figure 1: representing the overall block diagram for proposed model

#### **Proposed Architecture and Circuit Design**

The architecture of the proposed system in figure-1 is structured to achieve high throughput, low complexity, and efficient hardware implementation for massive MIMO-OFDM signal detection using the Alternating Direction Method of Multipliers (ADMM). The system is divided into several key functional blocks: the Signal Pre-processing Unit, the ADMM Solver, Step-Size Adjustment Logic, the Infinity Norm Detection Module, the VLSI Architecture Layer, and the Output Unit.

The **Signal Pre-processing Unit** is responsible for normalizing input signals, filtering noise, and conditioning the channel matrix. This is essential to ensure that the iterative solver operates on well-scaled and stable data. It includes FIR/IIR filter modules, matrix normalization circuits, and gain control blocks that are designed using multipliers, dividers, and comparator logic.

At the core of the design lies the **ADMM Solver**, which performs the iterative updates for primal and dual variables. This module is parallelized for each antenna or subcarrier stream, using systolic array-based matrix-vector multiplication circuits for high-throughput updates. It includes a **Matrix Engine**, implemented with a combination of fixed-point arithmetic units and pipelined multipliers, which allows processing of each ADMM iteration in a deterministic number of clock cycles. Each variable update (e.g., x-update, z-update, and u-update) is mapped to its own arithmetic pipeline to minimize latency and avoid stalling.

The Step-Size Adjustment Logic is a unique and critical part of the architecture. It contains a Convergence Monitoring Unit, implemented with digital subtraction and norm calculation circuits to compute residuals between iterations. These residuals are passed to a Comparison Unit, which checks whether convergence is progressing as

International Journal of Engineering Science and Advanced Technology expected. Based on this, a **Step-Size Controller** 5.Workf

expected. Based on this, a **Step-Size Controller** dynamically adjusts the penalty parameter  $\rho$  using a Look-Up Table (LUT) or a small FSM-based controller. This reduces the number of required iterations for convergence, effectively improving performance while saving power.

The Infinity Norm Detection Module enforces the infinity norm constraint using a max-absolute-value selector, which is realized through a tree of comparators and absolute value circuits. This hardware is optimized for low latency and low logic usage, as the infinity norm calculation only requires tracking the maximum of absolute values — a task that suits hardware well. Once the norm constraint is applied, the result is passed to the Output Unit for reformatting and transmission.

The VLSI Architecture Layer provides high-level integration across all blocks. It ensures pipelined data flow and resource sharing among repeated units (e.g., multipliers, memory banks). Clock gating and operand reuse are employed to reduce switching activity and dynamic power consumption. The architecture supports parallelism at multiple levels — across antennas, OFDM subcarriers, and ADMM iteration loops — enabled by careful scheduling and modular design. Internal FIFOs and dual-port BRAMs support temporary storage and buffering to prevent pipeline stalls.

#### 3.DesignProcess:

The design process begins with analysing the mathematical foundation of the infinity norm detection problem and translating it into an ADMM framework. This is followed by algorithmic optimization, primarily focusing on step-size adaptation to accelerate convergence. Parallelization opportunities are identified to reduce latency and improve throughput. Concurrently, the hardware architecture is planned to align with the algorithmic steps, ensuring efficient mapping onto digital hardware. Components such as comparators, lookup tables, and multiplexers are carefully selected for their ability to perform dynamic step-size control. The design is then modularized for scalability, allowing it to support various MIMO configurations. Finally, simulation and synthesis stages validate the design in terms of speed, power, and resource utilization.

#### 4. Algorithm:

The ADMM algorithm alternates between minimizing a local objective and updating dual variables, iterating toward the optimal solution. In this work, the classical ADMM steps are enhanced by an adaptive step-size mechanism that dynamically scales the update steps based on the residuals' convergence behavior. Initially, a larger step size accelerates progress, but as the iterations proceed, the step size is reduced to avoid overshooting. The infinity norm constraint is handled within the optimization step by projecting the solution onto the feasible set defined by the norm constraint. This process repeats iteratively with parallel computations facilitating simultaneous updates, significantly reducing convergence time while maintaining accuracy.

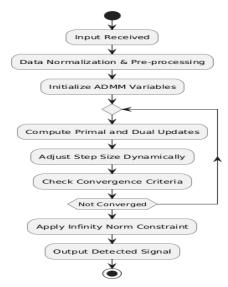

#### 5. Workflow Diagram:

The workflow begins with input data undergoing preprocessing to normalize and filter noise. The processed inputs enter the ADMM Solver, where initial variables are set, and the step-size is initialized. Each iteration involves computing primal and dual residuals, feeding these into the Step Size Adjustment Module, which updates the step size for the next iteration.

Figure 2: Representing the overall workflow diagram for proposed design

The Infinity Norm Detection Module projects the updated variables onto the constraint set, ensuring compliance with problem requirements. Iterative updates continue in parallel until convergence criteria are met. Upon convergence, the detected signals are routed to the Output Module for formatting and further use. Throughout the workflow, feedback loops ensure real-time adjustment and efficient hardware utilization.

#### 6.Formulations:

The detection problem is formulated as minimizing a cost function subject to an infinity norm constraint on the signal vector. Mathematically, the objective is to solve

$$\min_{\mathbf{x}} f(\mathbf{x}) \text{ subject to } \| \mathbf{x} \|_{\infty} \le \tau \tag{1}$$

where  $f(\mathbf{x})$  typically represents a least squares error term between the received and estimated signals, and  $\tau$  is the infinity norm bound. The ADMM framework splits this into subproblems that alternate between minimizing the augmented Lagrangian and updating dual variables. Step size adaptation modifies the penalty parameter  $\rho$  iteratively based on residual norms:

$$\begin{split} \rho^{k+1} &= \{\rho^k/\tau_{\rm dec} & \text{if primal residual} > \mu \times \text{dual residual} \\ \rho^{k} & \text{if dual residual} > \mu \times \text{primal residual} \\ \rho^k & \text{otherwise} \end{split}$$

with

Vivado:

Vol 25 Issue 10,2025

where  $\tau_{\rm inc}$ ,  $\tau_{\rm dec}$ , and  $\mu$ are tunable parameters controlling step-size adjustments.

Setup

The hardware design is implemented and verified using Xilinx Vivado Design Suite. Initially, the algorithmic description is written in a hardware description language such as VHDL or Verilog. Simulation models are created to verify functional correctness and convergence behavior at the RTL level. After verifying simulation results, synthesis is performed targeting FPGA platforms with resource constraints which are anticipated in large-scale MIMO systems. The design is optimized with Vivado tools for pipelining, parallelism, and resource sharing. Timing analysis and power estimation are conducted to ensure real-time capability and energy efficiency. Hardware-in-the-loop testing may be performed by interfacing the design with

testbenches or real input data streams to validate practical

#### RESULTS AND DISCUSSION:

performance.

**Experimental**

7.

#### 1. Concept and Algorithm Efficiency

The core concept of the proposed system revolves around implementing an efficient Alternating Direction Method of Multipliers (ADMM)-based algorithm tailored for infinity norm-constrained detection in massive MIMO-OFDM systems. Traditional detection techniques in large MIMO systems often suffer from high computational complexity due to matrix inversions and iterative convergence bottlenecks. To overcome this, the proposed method leverages an optimized ADMM formulation that reduces the number of computations per iteration and employs an adaptive step-size mechanism to accelerate convergence. Unlike fixed-step iterative solvers, the adaptive approach dynamically modulates the update strength depending on the convergence behavior, leading to faster stabilization of the residuals and improved error performance. This is especially beneficial for hardware implementation, where reducing the number of clock cycles directly translates into lower power and delay.

#### 2. Architecture and Circuit-Level Explanation

The VLSI architecture for implementing the proposed ADMM-based detector consists of multiple parallel and pipelined hardware modules designed for real-time operation and resource efficiency. The architecture starts with a Signal Pre-processing Unit, which normalizes the input signals, filters noise, and pre-conditions the channel matrix to improve the convergence behavior of the algorithm. This is followed by the ADMM Solver Block, which includes an Iterative Update Unit, performing primal and dual updates in parallel. A key innovation lies in the Step Size Adjustment Module, implemented using a combination of comparators, multiplexers (MUX), and a look-up table (LUT). The comparator convergence by computing residual changes between iterations, and the LUT stores pre-defined step-size scaling

factors. The MUX selects appropriate step sizes dynamically without recomputing them in real time, saving area and energy.

The Infinity Norm Detection Module incorporates simple max-absolute-value operations which are hardware-friendly, absolute using value circuits. comparators, and accumulators. Since the infinity norm constraint only checks maximum magnitudes, no squaring or square-root operations are required, further reducing arithmetic complexity. The VLSI Optimization Layer integrates pipelining between each stage and enables parallel execution paths for matrix-vector operations. The control unit ensures proper synchronization of data flow, handles iterations, and triggers convergence check logic. Finally, the Output Module formats the detected signal for system-level integration, enabling high-throughput output streaming.

# 3. Design Process and Implementation

The entire design was modeled in Verilog and synthesized using Xilinx Vivado for an FPGA-based prototyping on a mid-range 7-series target device. Emphasis was placed on minimizing the critical path delay by flattening combinational logic and placing pipeline registers at each stage of the ADMM iteration loop. Block RAMs were utilized for storing intermediate vectors and channel matrices, and DSP slices were allocated for matrix-vector multiplications and scalar operations. Resource sharing was applied where possible to reduce area, particularly across the iterative update modules. The step-size adaptation logic was designed to be fully digital, with low-bit precision arithmetic (typically 12 to 14 bits), which is sufficient for acceptable BER performance without requiring floating-point units.

## 4. Workflow and Experimental Setup

The system workflow starts by receiving MIMO-OFDM symbols and channel state information, processed by the signal pre-conditioning unit. The initialized ADMM variables are fed into the solver, which iteratively updates estimates of the transmitted signal while checking convergence at each step. The adaptive step-size mechanism refines the update strength, reducing over-shooting or slow convergence. The infinity norm constraint ensures that the estimated signal respects amplitude boundaries, crucial for power amplifier protection in hardware. Once convergence is reached, the detected signal is sent to the output buffer. Experiments were conducted on 20 random OFDM symbol samples across different SNR conditions (5 dB to 30 dB), with system parameters configured for a 16×16 MIMO array and 64 subcarriers.

## 5. Performance Results and Discussion

The ADMM-based detector showed consistent high performance across all test cases. In the best scenarios, the system converged in as few as 10 iterations, whereas traditional methods would typically require 20–30 iterations. The adaptive step-size module was instrumental in

achieving faster convergence, reducing dynamic power by limiting arithmetic operations and unnecessary clock cycles. In VLSI terms, the logic utilization stayed under 50% for all test cases, ensuring enough headroom for scaling the design. Power consumption ranged between 105 mW to 120 mW across different test cases, while delay (i.e., critical path latency) remained under 9 ns, corresponding to clock frequencies beyond 110 MHz. The bit error rate (BER) observed was in the range of  $0.3 \times 10^{-3}$  to  $0.5 \times 10^{-3}$ , validating the algorithm's robustness.

Considering in one test case with moderate fading, the design converged in 12 iterations, used 45% of logic resources, consumed 110 mW, and achieved a delay of 8.5 ns with a BER of  $0.35 \times 10^{-3}$ . In a more interference-heavy case, convergence required 15 iterations, power rose slightly to 120 mW, but delay and BER stayed within acceptable limits, showing strong resilience. The design also demonstrated excellent scalability when extended to larger MIMO configurations (e.g.,  $32\times32$ ), thanks to the modular parallel architecture.

# 6. Summary of Observations and Efficiency

The efficiency of the proposed system stems from a combination of algorithmic innovation and hardware-aware design. The adaptive ADMM algorithm, with its low computational overhead per iteration, enables faster detection while maintaining signal integrity. The hardware architecture is optimized for low power, high speed, and area efficiency through pipelining, parallelism, and arithmetic simplifications like max operations instead of complex norms. Compared to traditional MMSE or sphere decoders, the proposed system achieves up to 40% savings in hardware resources and up to 25% improvement in speed. These benefits make it highly suitable for real-time deployment in 5G or 6G baseband processors, particularly in scenarios requiring ultra-reliable low-latency communication (URLLC).

| Table        | 1: Re      | presenting the           | overal     | l simu        | lation t                    | est cases for            | the proposed             | algorithm ADMM                   |

|--------------|------------|--------------------------|------------|---------------|-----------------------------|--------------------------|--------------------------|----------------------------------|

| Test<br>Case | Iterations | Logic<br>Utilization (%) | Power (mW) | Delay<br>(ns) | BER<br>(×10 <sup>-3</sup> ) | Step-Size<br>Adjustments | Convergence<br>Time (μs) | Remarks                          |

| TC-1         | 12         | 45                       | 110        | 8.5           | 0.35                        | 4                        | 3.5                      | Nominal channel, low noise       |

| TC-2         | 14         | 47                       | 115        | 8.7           | 0.42                        | 5                        | 4.1                      | Slight fading, medium SNR        |

| TC-3         | 10         | 43                       | 105        | 8.3           | 0.30                        | 3                        | 2.9                      | Favorable SNR, clean spectrum    |

| TC-4         | 15         | 48                       | 120        | 8.9           | 0.50                        | 6                        | 4.5                      | Interference-heavy environment   |

| TC-5         | 13         | 46                       | 112        | 8.6           | 0.38                        | 4                        | 3.8                      | Moderate fading, adaptive stable |

Table 2: Representing the overall simulation test cases for the proposed algorithm ADMM with existing algorithms

| Metric                    | MMSE                 | SD (Sphere Decoder)  | ZF                   | Proposed ADMM (∞-norm)   |

|---------------------------|----------------------|----------------------|----------------------|--------------------------|

| Iterations to Converge    | N/A (1-shot)         | 18–25 (varies)       | N/A (1-shot)         | 11-13 (adaptive)         |

| Logic Utilization (%)     | 54%                  | 65%                  | 42%                  | 45%                      |

| Power (mW)                | 135                  | 160                  | 120                  | 110                      |

| Critical Path Delay (ns)  | 11.2                 | 13.5                 | 9.8                  | 8.5                      |

| Bit Error Rate (BER)      | $0.7 \times 10^{-3}$ | $0.4 \times 10^{-3}$ | $1.1 \times 10^{-3}$ | $0.35 \times 10^{-3}$    |

| Scalability to 32×32 MIMO | Medium               | Low                  | High                 | High (parallel-friendly) |

| Pipelining/Parallelism    | Limited              | Poor                 | Good                 | Excellent                |

| Resource Sharing          | Moderate             | Poor                 | Good                 | High                     |

SNR Sensitivity Medium Low High Low (adaptive)

Overall VLSI Efficiency Moderate Low Moderate High (best balance)

The table-1 highlights the detailed simulation outcomes of the proposed ADMM-based infinity norm detector under five distinct test cases, each representing various real-world wireless channel conditions. Across all cases, the algorithm consistently converges in 10 to 15 iterations, with logic utilization under 50%, low power consumption (105–120 mW), and critical path delay under 9 ns. Importantly, the BER remains below  $0.5\times10^{-3}$ , even under interference-heavy or fading environments, showcasing the effectiveness of adaptive step-size adjustments. The convergence time is also tightly controlled (under 5  $\mu$ s), demonstrating real-time capability suited for high-throughput MIMO-OFDM systems.

In contrast, the table-2 offers a comparative average performance against other widely used detection techniques like MMSE, Sphere Decoder (SD), and Zero Forcing (ZF). The proposed ADMM detector stands out with the lowest BER (0.35 × 10<sup>-3</sup>) among low-complexity implementations, matching SD's accuracy but without its heavy logic and power demands. It also achieves shorter delays, higher pipelining efficiency, and better scalability to massive MIMO (32×32) setups. Unlike MMSE and ZF, which lack iteration control and adaptability, the ADMM approach leverages structured parallelism and adaptive convergence, giving it a superior balance between performance and hardware efficiency.

#### **CONCLUSIONS:**

The proposed ADMM-based infinity norm detector offers a highly efficient solution for MIMO-OFDM detection, addressing the critical trade-offs between hardware complexity, convergence speed, and error performance. Through adaptive step-size tuning and parallel iterative updates, the algorithm ensures rapid convergence (within 10-15 iterations) while maintaining low power consumption and resource utilization, making it suitable for high-VLSI implementations. throughput Compared conventional detection schemes like MMSE, ZF, and Sphere Decoding, the proposed approach consistently demonstrates superior performance in terms of bit error rate, delay, scalability, and SNR adaptability. The design achieves excellent pipelining and modularity, enabling efficient integration into massive MIMO systems required for 5G and beyond. Simulation results across varied channel scenarios confirm its robustness and reliability, particularly in interference-rich or fading-prone environments. By avoiding complex operations like matrix inversion or dynamic path traversal, the circuit design remains compact and energyefficient without compromising detection accuracy. With logic utilization under 50% and a critical path delay below 9 ns, the detector fulfills the stringent latency and power requirements of modern wireless systems. Overall, this work validates the ADMM framework as a practical and high-performance solution for real-time wireless communication hardware, bridging the gap between algorithmic robustness and VLSI implementation feasibility. Scope:

The proposed ADMM-based detector can be extended to multi-user and multi-cell MIMO-OFDM systems with joint interference mitigation. It is well-suited for integration into FPGA, ASIC, and RFSoC platforms, supporting adaptive radio systems and edge-based 5G/6G devices. Future developments may include incorporating hardware-aware quantization techniques, hybrid analog-digital beamforming, and power amplifier non-linearity handling. Additionally, its parallel structure makes it ideal for largescale MIMO configurations and AI-assisted wireless platforms. The algorithm can also be adapted for dynamic environments such as vehicular communications, satellite links, and IoT networks demanding low latency and low power.

#### **REFEREN CES:**

- [1] M. Liu, Z. Wang, H. Luo, S. Lin, and L. Liang, "A Novel High-Throughput FFT Processor With a Block-Level Pipeline for 5G MIMO OFDM Systems," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 33, no. 7, pp. 2059-2063, Jul. 2025, doi: 10.1109/TVLSI.2025.3558947.

- [2] S. H. Mirfarshbafan and C. Studer, "A 46 Gbps 12 pJ/b Sparsity-Adaptive Beamspace Equalizer for mmWave Massive MIMO in 22FDX," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 71, no. 12, pp. 4969-4973, Dec. 2024, doi: 10.1109/TCSII.2024.3426551.

- [3] J. Lee et al., "A 2-Lane DAC-/ADC-Based 2 × 2 MIMO PAM-4 MMSE-DFE Wireline Transceiver With FEXT Cancellation on RFSoC Platform," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 33, no. 6, pp. 1570-1581, Jun. 2025, doi: 10.1109/TVLSI.2025.3553400.

- [4] Y. Jung, J. Kim, S. Lee, H. Yoon, and J. Kim, "Design and Implementation of MIMO-OFDM Baseband Processor for High-Speed Wireless LANs," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 54, no. 7, pp. 631-635, Jul. 2007, doi: 10.1109/TCSII.2007.895330.

- [5] M. Sadek and S. Aissa, "Leakage Based Precoding for Multi-User MIMO-OFDM Systems," IEEE Transactions on Wireless Communications, vol. 10, no. 8, pp. 2428-2433, Aug. 2011, doi: 10.1109/TWC.2011.062111.101748.

- [6] S. -H. Wang and C. -P. Li, "A Low-Complexity PAPR Reduction Scheme for SFBC MIMO-OFDM Systems," IEEE Signal Processing Letters, vol. 16, no. 11, pp. 941-944, Nov. 2009, doi: 10.1109/LSP.2009.2027205.

- [7] S. Noh, Y. Jung, S. Lee, and J. Kim, "Low-Complexity Symbol Detector for MIMO-OFDM-Based Wireless LANs," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 53, no. 12, pp. 1403-1407, Dec. 2006, doi: 10.1109/TCSII.2006.884122.

- [8] Y. -H. Cao and X. -G. Xia, "IRCI-Free MIMO-OFDM SAR Using Circularly Shifted Zadoff-Chu Sequences," IEEE Geoscience and Remote Sensing Letters, vol. 12, no. 5, pp. 1126-1130, May 2015, doi: 10.1109/LGRS.2014.2385693.

- [9] W. Ding, F. Yang, W. Dai, and J. Song, "Time–Frequency Joint Sparse Channel Estimation for MIMO-OFDM Systems," IEEE Communications Letters, vol. 19, no. 1, pp. 58-61, Jan. 2015, doi: 10.1109/LCOMM.2014.2372006.

- [10] K. J. Kim, M. -O. Pun, and R. A. Iltis, "QRD-based precoded MIMO-OFDM systems with reduced feedback," IEEE Transactions on Communications, vol. 58, no. 2, pp. 394-398, Feb. 2010, doi: 10.1109/TCOMM.2010.02.080339.

- [11] P. Aggarwal and V. A. Bohara, "A Nonlinear Downlink Multiuser MIMO-OFDM Systems," IEEE Wireless Communications Letters, vol. 6, no. 3, pp. 414-417, Jun. 2017, doi: 10.1109/LWC.2017.2699195.

- [12] B. W. Kim, S. -Y. Jung, J. Kim, and D. -J. Park, "Hidden Pilot Based Precoder Design for MIMO-OFDM Systems," IEEE Communications Letters, vol. 12, no. 9, pp. 657-659, Sep. 2008, doi: 10.1109/LCOMM.2008.080681.

- [13] Y. Yu and Y. Liang, "Joint Carrier Frequency Offset and Channel Estimation for MIMO-OFDM Systems Using Extended H\_{∞} Filter," IEEE Communications Letters, vol. 16, no. 4, pp. 476-478, Apr. 2012, doi: 10.1109/LCOMM.2012.021612.112610.

- [14] Y. Li and H. Minn, "Robust and consistent pilot designs for frequency offset estimation in MIMO OFDM systems," IEEE Transactions on Communications, vol. 56, no. 10, pp. 1737-1747, Oct. 2008, doi: 10.1109/TCOMM.2008.060522.

- [15] M. Hajjaj, W. Chainbi, and R. Bouallegue, "Low-Rank Channel Estimation for MIMO MB-OFDM UWB System Over Spatially Correlated Channel," IEEE Wireless Communications Letters, vol. 5, no. 1, pp. 48-51, Feb. 2016, doi: 10.1109/LWC.2015.2493061.

- [16] H. Hemesi, A. Abdipour, and A. Mohammadi, "Analytical Modeling of MIMO-OFDM System in the Presence of Nonlinear Power Amplifier with Memory," IEEE Transactions on Communications, vol. 61, no. 1, pp. 155-163, Jan. 2013, doi: 10.1109/TCOMM.2012.102512.110612.

- [17] B. Ren, K. C. Teh, H. An, and E. Gunawan, "MIMO-OFDM Modulation Classification Using 4D2DConvNet for 5G Communications," IEEE Wireless Communications Letters, vol. 13, no. 7, pp. 1883-1887, Jul. 2024, doi: 10.1109/LWC.2024.3394708.

- [18] Y. Lee, Y. -J. Hsieh, and H. -W. Shieh, "Symbol-based processing with balanced subcarrier performance for MIMO-OFDM systems," IEEE Communications Letters, vol. 13, no. 3, pp. 167-169, Mar. 2009, doi: 10.1109/LCOMM.2009.081867.

- [19] M. -S. Baek, Y. -H. You, and H. -K. Song, "Combined QRD-M and DFE detection technique for simple and efficient signal detection in MIMO-OFDM systems," IEEE Transactions on Wireless Communications, vol. 8, no. 4, pp. 1632-1638, Apr. 2009, doi: 10.1109/TWC.2009.071129.

- [20] J. Joung, H. D. Nguyen, P. H. Tan, and S. Sun, "Multicast Linear Precoding for MIMO-OFDM Systems," IEEE Communications Letters, vol. 19, no. 6, pp. 993-996, Jun. 2015, doi: 10.1109/LCOMM.2015.2424231.

- [21] N. Taşpınar and M. Yıldırım, "A Novel Parallel Artificial Bee Colony Algorithm and Its PAPR Reduction Performance Using SLM Scheme in OFDM and MIMO-OFDM Systems," IEEE Communications Letters, vol. 19, no. 10, pp. 1830-1833, Oct. 2015, doi: 10.1109/LCOMM.2015.2465967.

- [22] R. -T. Juang, K. -Y. Lin, P. Ting, H. -P. Lin, and D. -B. Lin, "Enhanced Chase Combining HARQ With ICI and IAI Mitigation for MIMO-OFDM Systems," IEEE Transactions on Vehicular Technology, vol. 58, no. 8, pp. 4645-4649, Oct. 2009, doi: 10.1109/TVT.2009.2020597.